Peer Reviewed Journal ISSN 2581-7795

## Harmonic Analysis in Seventeen Level Cascaded H-Bridge Inverter Using Carrier based Modulation Techniques

Subham, Santosh S. Negi

Department of Electrical& Electronics Engineering, RKDF Institute of Science and Technology SRK University Bhopal M.P.

Abstract- In this paper various multicarrier PWM schemes are proposed, which can reduce the THD and enhance the output voltages waveform from seventeen level inverter. Here, three modulation techniques are compared; constant switching frequency(CSF), Phase shift(PS PWM) and variable switching frequency (VSF). These schemes are applied for analysis of both symmetrical and asymmetrical structure of 17-level cascaded H-bridge multilevel inverter (CHB MLI). Simulation for 17- level CHB MLI has been carried out in MATLAB/ Simulink and simulation results for voltage waveform and harmonic spectrum are presented in this paper and compared.

Keywords-- Cascaded MLI; Symmetrical MLI; Asymmetrical MLI;Constant Switching Frequency; Phase Shift PWM and Variable Switching Frequency PWM ;Total Harmonic Distortion

#### 1. INTRODUCTION

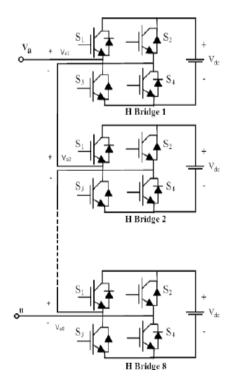

Multilevel inverters have achieved increasing acceptance in high-performance applications. Recently, for high power application, multilevel converters are widely used such as static var compensators, drives and active power filters. The advantages of multilevel inverters are good power quality, low switching loss and highvoltage capability [1-3]. The topologies of multilevel inverters are classified into three types; the flying capacitor, diode clamped and cascaded multilevel inverters [4-8]. The cascaded H-bridge multilevel inverter is widely used due to the modularity and simplicity of the control. The single-phase cascaded multilevel inverter is shown in Fig. (1). the circuit is designed for a seventeen level inverter consisting of eight H-bridge and 32 switches. Each dc source connected with their respective H-bridges generates three different output voltages, +V<sub>dc</sub>, 0 and -V<sub>dc</sub> using various combinations of switching with the 4 switches. The output voltage of multilevel inverter is synthesised by H-bridge connected in series. The number of output phase voltage levels in cascaded inverter as m = 2s+1, where s is the number of separate dc sources and m is the no, of levels in inverter output voltage. The cascaded H-bridge MLI are mainly classified into

two ways; symmetric and asymmetric structure. It depends on the magnitude of the DC source voltages. Symmetric CMLI is obtained with same magnitude of dc source voltages and asymmetric CMLIwith different magnitude dc source voltages [9]-[10]. In this paper, constant switching frequency, variable switching frequency carrier pulse width modulation methods are presented. These modulation methods give advantages in multilevel inverter to minimise the percentage of total harmonic distortion (THD)and increases the output voltage. The THD values are low in symmetric structure compared those in asymmetric MLI, but output voltage is high the actual value.

Fig.1 Seventeen level single phase cascaded H-bridge inverter

#### 2.CONSTANT SWITCHING FREQUENCY PWM

The constant switchingfrequency (CSF) pulsewidth modulation (PWM) technique is the one of most popular and very simple switching techniques for power semiconductor devices. In m-level

Peer Reviewed Journal ISSN 2581-7795

inverter, (m-1) carriers with the same frequency  $f_c$ and the same amplitude  $A_c$  are disposed such that the bands they occupy are continuous. The reference waveform has peak-to-peak amplitude  $A_m$ , the frequency  $f_m$  which is zero centred in the middle of the carrier set. The reference is continuously compared with each of the carrier signals. If the reference is greater than s carrier signal, then the active device corresponding to that carrier is switched off. In multilevel inverters, the amplitude modulation index  $M_i$  and the frequency ratio  $M_f$  are defined as

$$M_i = \frac{A_m}{(m-1)A_c} (1)$$

$$M_f = \frac{f_c}{f_m} (2)$$

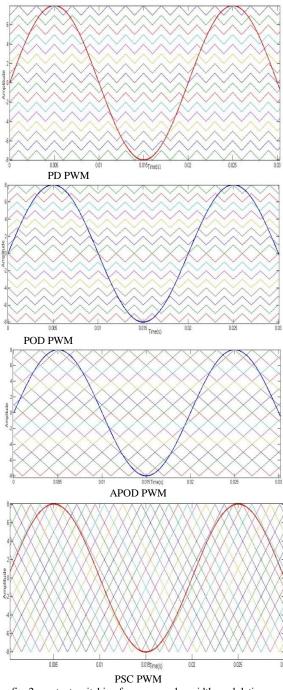

In this constant switching frequency pulse width modulation method also known as level-shift modulation, related to the way the carrier waves are placed in relation to the reference signal, three cases can be distinguished. Fig. 2a shows a phase disposition pulse-width modulation (PDPWM), where all the carriers are in phase. Fig. 2b shows a opposition disposition phase pulse-width modulation (PODPWM), where the carriers above the zero reference are in phase, but shifted by 180 degree from those carriers below the zero reference. Fig. 2c shows an alternative phase opposition disposition (APODPWM), where each carrier band is shifted by 180 degree from the adjacent bands.

#### 2.1 Phase shift carrier PWM

Phase shift carrier (PSC) PWM is one kind of constant switching frequency PWM technique. In this PWM scheme, all the triangular carriers have the same frequency and same peak-peak amplitude, but there is a phase shift between any two adjacent carrier waves. For m level voltage, (m-1) carrier signals are required and they are phase shifted with an angle of 90 degree from the adjacent bands shown in Fig. 2d.

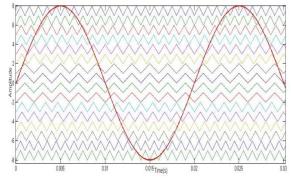

# 3.VARIABLE SWITCHING FREQUENCY PWM

This technique uses the conventional sinusoidal reference signal and the (m-1) carrier signals with variable frequency. For the 9 level inverter there are 8 distinct carriers with variable frequency and same magnitude. This modulation method signifies that harmonic energy is concentrated at carrier frequency. Carriers of the 9-level inverter with variable switching frequency of 2 kHz- 5 kHz are shown in Fig. 3.

fig. 2 constant switching frequency pulse width modulation

Fig. 3 Variable switching frequency pulse width modulation

### Peer Reviewed Journal ISSN 2581-7795

#### 4. **RESULTS**

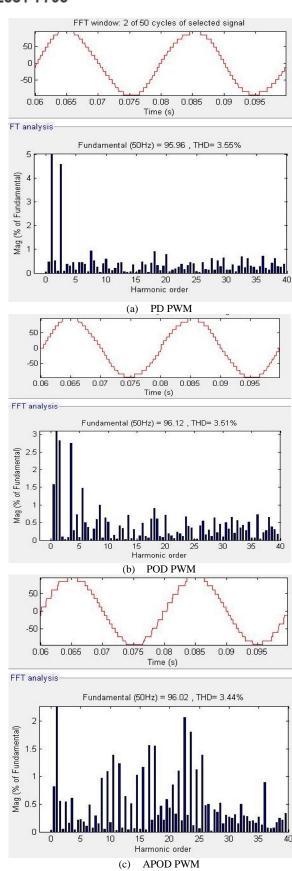

The percentage of THD and output voltage values using constant switching frequency (CSF PWM), phase shift (PS PWM) and variable switching frequency (VSF PWM) for symmetrical and asymmetrical multilevel inverter are given in table 1.

| Table. 1                                  |                 |          |                     |          |

|-------------------------------------------|-----------------|----------|---------------------|----------|

| PWM Methods                               | Symmetrical MLI |          | Asymmetrical<br>MLI |          |

|                                           | Voltage(V)      | %<br>THD | Voltage(<br>V)      | %<br>THD |

| Const.<br>Switching Freq.                 |                 |          |                     |          |

| PD                                        | 95.96           | 3.55     | 98.91               | 4.88     |

| POD                                       | 96.12           | 3.51     | 99.07               | 4.90     |

| APOD                                      | 96.02           | 3.44     | 98.93               | 4.73     |

| Phase shift<br>PWM                        | 97.74           | 6.09     | 97.76               | 6.77     |

| Variable<br>Switching<br>Frequency<br>PWM | 96.01           | 4.77     | 98.97               | 5.73     |

#### 4.1. Simulation Results

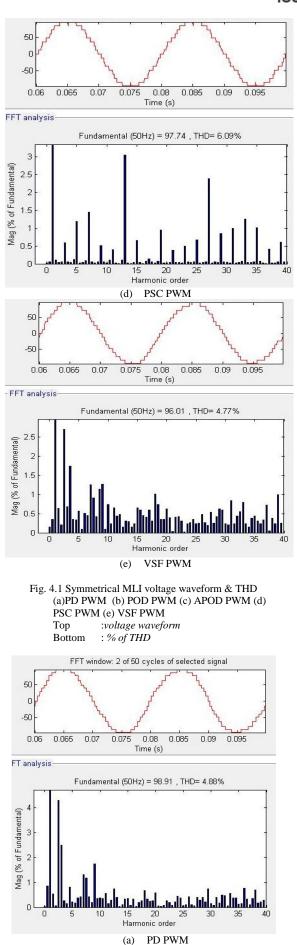

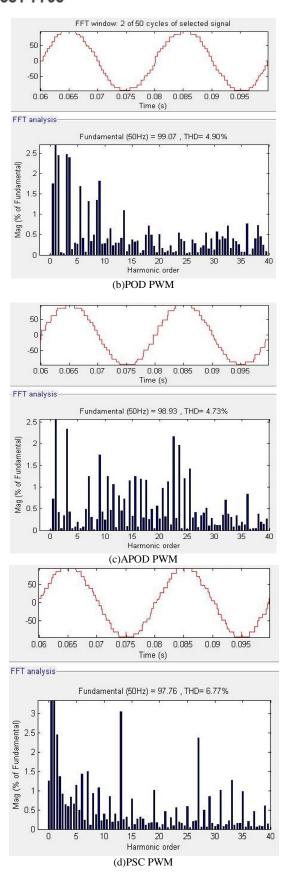

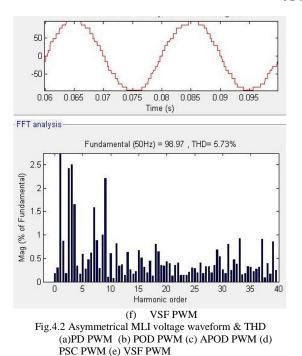

To verify the proposed carrier based PWM methods, a simulation model for single phase cascaded H bridge seventeen level inverter is implemented for symmetrical and asymmetrical structure. Eight identical dc sources of 12V are used for symmetric structure and 8 different dc sources whose sum is 96V is used for asymmetric structure. The voltage waveform and % of THD using different PWM schemes are shown in Fig. 4.1 (a),(b),(c),(d),(e) for symmetrical MLI and Fig. 4.2 (a),(b),(c),(d),(e) for asymmetrical MLI, respectively.

Peer Reviewed Journal ISSN 2581-7795

Peer Reviewed Journal ISSN 2581-7795

Top

Bottom

From the simulation results it is seen the % THD is less in CSF PWM whereas corresponding values are high in VSF PWM and PSC PWM for both symmetrical and symmetrical MLI. The RMS value of fundamental output voltage is significantly higher (97.76V) in the proposed PSC PWM technique compared to other methods, except POD PWM. The cascaded H-bridge seventeenlevel inverter with proposed PSC PWM gives more output voltage and minimised the THD and voltage stress on semiconductor switches.

: voltage waveform

:% of THD

#### REFERENCES

- J.S. Lai, F.Z. Peng, "Multilevel converters a new bread of converters", *IEEE Trans. Ind. Appl.*, 1996, 32, pp. 509– 517,1996

- [2] R. Teodorescu, F. Blaabjerg, J.K. Pedersen, E. Cengelci, P.N. Enjeti, "Multilevel inverter by cascading industrial VSI", *IEEE Trans. Ind. Electron.*, 49, pp. 832–838,2002

- [3] P. Palanivel, S.S. Dash "Analysis of THD and output voltage performance for cascaded multilevelinverter using carrier pulse width modulation technique" *IET Power Electronics vol. 4, no. 8, pp. 951-958, 2010*

- [4] J. Rodriguez, J.S. Lai, F. Zheng Peng, "Multilevel inverters; a survey of topologies, controls, and applications", *IEEE Trans. Ind. Electron.*,49, pp. 724– 738,2002

- [5] L.M. Tolber, T.G. Habetler, "Novel multilevel inverter carrier basedPWM method", *IEEE Ind. Appl.*, 35, pp. 1098–1107, 1999.

- [6] B. P. McGrath, D. G. Holmes, T.Meynard "Reduced PWM harmonic distortion for multilevel inverter operating over a wide modulation range", *IEEE Trans. Power Electron.*, 2006, 21, pp. 941–949

- [7] S. S. Barah and S. Behera, "An Optimize Configuration of H-Bridge Multilevel Inverter," 2021 1st International Conference on Power Electronics and Energy (ICPEE), 2021, pp. 1-4,

- [8]R. Naderi, A. Rahmati, "Phase-shifted carrier PWM technique for general cascaded inverters", *IEEE Trans. Power Electron.*, 2008, 23, pp. 1257–1269

- [9] O. L. Jimenez, R. A. Vargas, J. Aguayo "THD in Cascade Multilevel Inverters Symmetric and Asymmetric" 2011ERAMC IEEE computersociety, pp.289-295, 2011

- [10] Z. E. Abdulhamed, A. H. Esuri and N. A. Abodhir, "New Topology Of Asymmetrical Nine-Level Cascaded Hybrid Bridge Multilevel Inverter," 2021 IEEE 1st International Maghreb Meeting of the Conference on Sciences and Techniques of Automatic Control and Computer Engineering MI-STA, 2021